インテル® Itanium® プロセッサーは、HPE社とインテルが共同で開発したEPIC(Explicitly Parallel Instruction Computing:明示的並列命令コンピューティング)アーキテクチャを実装した64ビットマイクロプロセッサーです。EPICはCISC、RISCと発展してきたマイクロプロセッサー・アーキテクチャが将来パフォーマンスアップをする上で直面するであろう困難を回避するために考えられたアーキテクチャです。

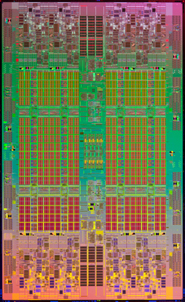

最新のインテル® Itanium® プロセッサー9700製品ファミリーは、9500製品ファミリーのマイクロアーキテクチャーを継承、31億個のトランジスタ、8つのコアを搭載。

インテル® Itanium® プロセッサー9700/9500製品ファミリーのRAS機能。

| 機能 | 9300番台 | 9500製品ファミリー | 9700製品ファミリー |

|---|---|---|---|

| L3キャッシュの エラー検出・訂正機能 |

△ 2ビットエラーの検出 1ビットエラーの訂正 |

○ 3ビットエラーの検出 2ビットエラーの訂正 |

○ 3ビットエラーの検出 2ビットエラーの訂正 |

| 命令の再実行機能 | - | ○ | ○ |

製造プロセスルールの微細化にともない、キャッシュエラーの検出・訂正機能を強化しています。9700/9500製品ファミリーでは、L3キャッシュのエラー検出・訂正機能を、従来の2ビットのエラー検出、 1ビットのエラー訂正から、3ビットのエラー検出、 2ビットのエラー訂正に強化しています。

インテル®Itanium®プロセッサー9700/9500製品ファミリーでは、命令の再実行機能を採用しており、命令実行中にエラーが発生したことを検知すると命令の再実行を自動的におこないます。この機能はメインフレーム等に搭載されていた高度な機能であり、システム停止を回避することが可能になり、ミッションクリティカル業務での安全性を高めることに役立ちます。